Wiznet Ethernet Chip Design Guide

Introduction This document is a Design Guide for WIZnet Chip to be used for PCB. It contains reference for PCB design using W5100, W5300, W5500, W7100A, W7500, and W7500P. Contents of MDI (Medium-de..

alanp.tistory.com

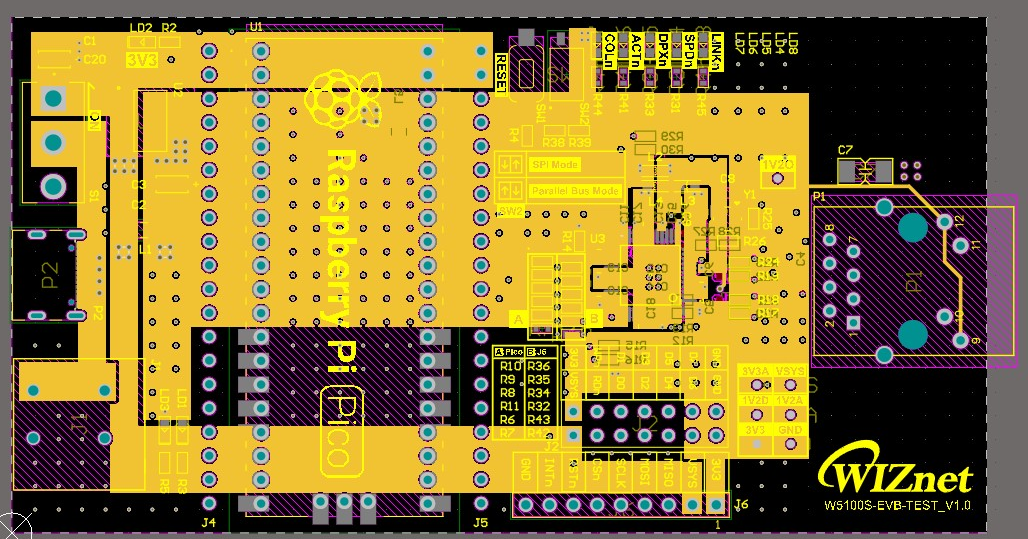

위의 Wiznet Ethertnet Chip Design Guide 를 작성하기 위해 (유저에게 Recommend 해줄 수 있는 실물 PCB 를 제작) , 제작 보드로 Chip 공부하기 위해 이 보드를 제작하게 되었다.

툴은 Altium 을 사용했는데, 처음 배우면서 사용하는지라 설계, 제작하는데 시간이 꽤나 소요됐다.

보드이름은 W5100S-EVB-TEST 보드라고 지었다.

회로도 작성이 완료됐다. 가능한한 Pin 을 전부 헤더로 뽑고 싶어서 헤더가 조금 많이 사용됐다. 해당 보드는 W5100S 에 라즈베리파이 피코를 장착하여 사용할 수도 있고, 다른 MCU 를 연결하여 사용할 수 도 있게 설계했다.

전원은 흔히 많이 사용하는 USB C Type 을 이용하여 사용할 수도 있고, 오디오 커넥터(?)스프링 커넥터(?) 로도 쉽게 사용할 수 있도록 설계했다.

KF142R-5.08-2P

전원은 5V, 3.3V 를 사용하는데 3.3V 가 생각보다 전류가 많이 들어갈 수 있으니, 용량이 조금큰 AMS1117 를 사용하기로 했다.

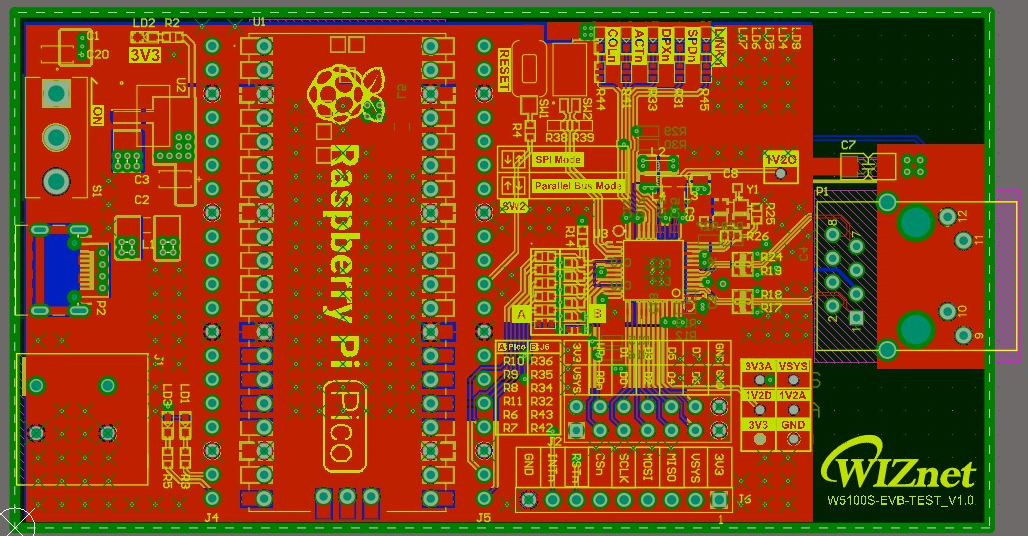

Artwork 을 완료를 한 모습니다. 1 -TOP, 2-GND, 3-PWR, 4- BOTTOM 으로 설계했는데 파워층에서 꽤나 고전했다.

다시봐도 너무 이쁘게 안나온것 같아서 눈살이 찌푸려진다.

전체 레이어를 덮은 모습이다. 누군가는 알겠지만 여기엔 아주 큰 오류가 있다. 밑에서 따로 다루기로 하겠다.

완성본의 3D 모습인데, 이 모습은 생각보다 이쁘게 잘 나온 것 같다.

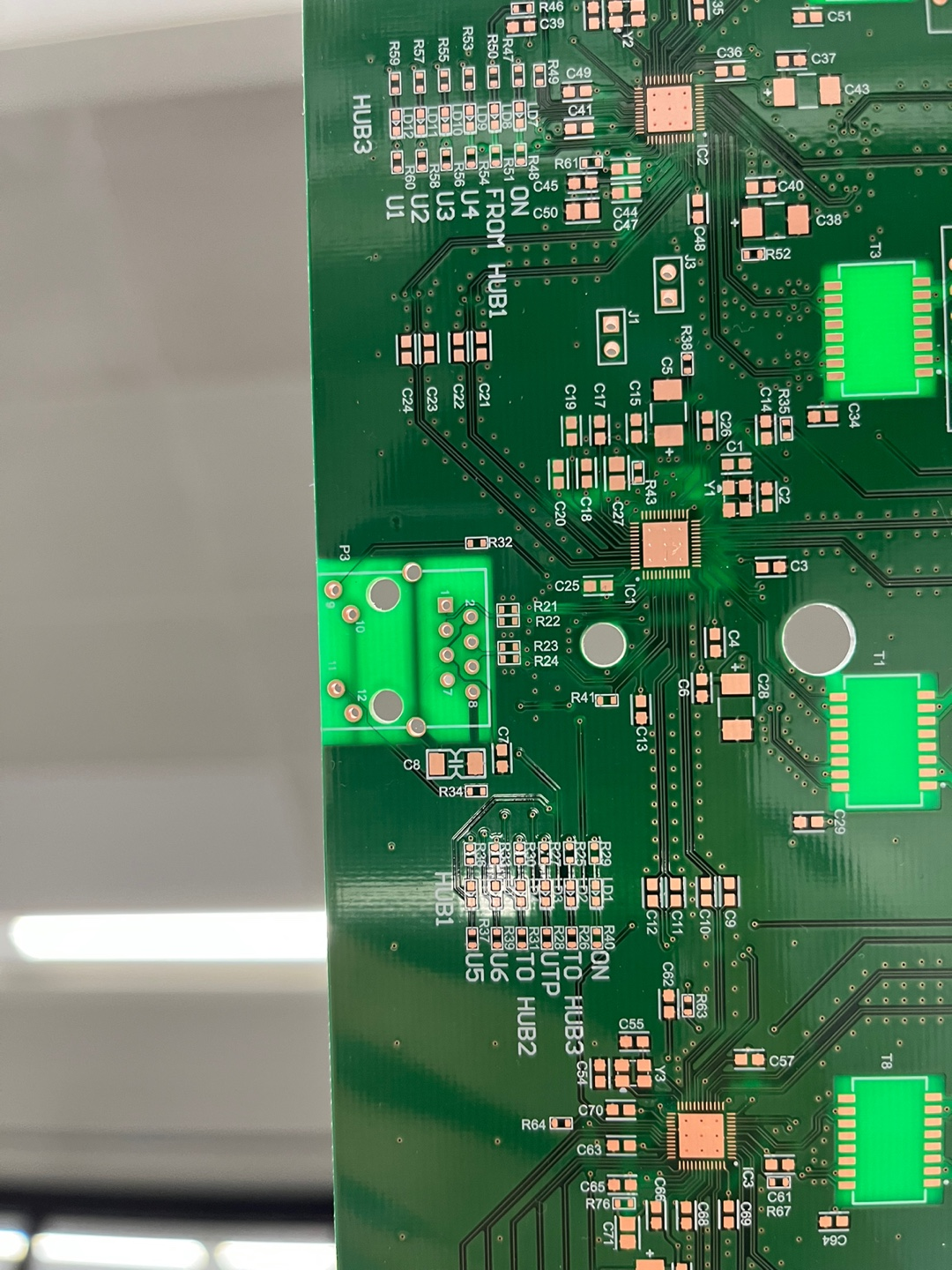

발주는 한샘디지텍에서 진행했고 2박 3일 걸려 도착했다. 4층 기본이 3박 4일인걸 감안하면 굉장히 빨리왔다.

보드가 도착했다. 나름 잘 나온 것 같다.

일단 조립은 다음에~~

자 여기서 설계의 가장 큰 오류를 다뤄보도록 하겠다.

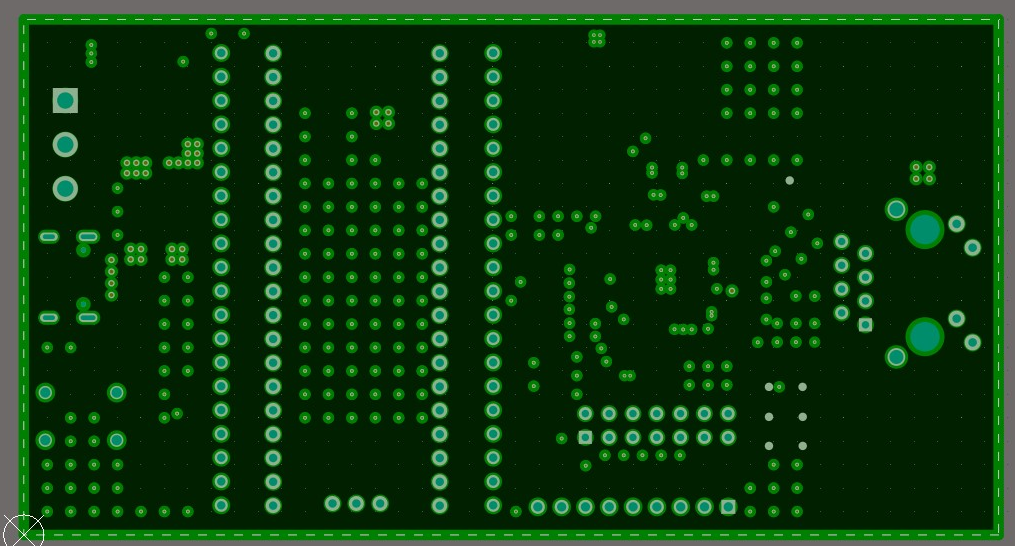

아까 위에서 봤던 설계이미지를 보면 딱 알겠지만 GND 층의 RJ-45 단의 GND 분리가 안되어있다.

PCB 를 빛에 비춰보니 환하게 비춰지지가 않는다. 원래 저부분은 아에 카파가 깔리지 않도록 설계했던 부분인데, 이너쪽에 무언가가 깔려있다.

다른보드 / 원래는 아무것도 깔리지 않으면 이렇게 환하게 보여야함

이 보드와 비교해봐도 명확하게 알 수 있다.

허겁지겁 설계파일을 보니 맙소사다. GND 전체가 다 깔려있다...

해당 GND 층을 Signal 로 설계했었다가 막판에 다른 설계 파일들을 보며 Plane 으로 변경하고 "오 이렇게 간단하게 전체 카파를 깔 수 있구나~" 했었던 것이 패착이었다. GND , CHGND 를 구분지었던 것을 까먹었던 것.

다시 해당 층을 Signal 층으로 바꾸니

이렇게 원래 설계했던대로 나왔다...

참 바보같은 행동이었지만 공부가 되었다고 생각하기로 한다.

그리고 또 하나의 반전(?) 은 Plane 을 해주면 Plnae 의 넷트 속성을 설정해주어야 연결이 되는데, 나는 Plane 이름만 GND로 설정하여 실제 GND 연결은 되지 않았다. 즉 GND 층은 텅텅 빈 층이라는것....

저 위의 이미지만 봐도 GND 가 연결되어있지 않다는 것을 알 수 있다.

층을 Plane 으로 설정한다면

더블 클릭하여 해당 층의 넷트 속성을 넣어주도록 한다.

그러면 이렇게 GND 가 X 표시로 연결되게 된다.

여기서 멈추지 않고, 당연히 이상태에서 GND 구분을 해보도록 한다.

Polygpn Cutout 으로 까주면 될 것으로 생각하는데, 해당 층에서는 Polygon 버튼이 먹질 않는다. (왜 그런지는 모르겠음)

그래서 다른 층에서 Cutout 을 만들어 속성변경으로 해당층으로 바꿔주니

이렇게 원하는 부분이 깎이는 모습이다.

여기서 이제 CHGND 만 따로 넣어주면 되는데.

한참을 어떻게 해야하지 고민하고 찾아본 결과, 애초에 접근방법이 잘못되었다는 것을 알게 되었다.

Plane 설정은 애초에 2가지 속성의 카파를 깔 수 없다는 것.. 애초에 목적이 전체를 덮는것이 목적이니 그런가 싶다.

(참으로 아쉬운 기능이 아닐 수 없다... 제가 잘 못 파악한 것이라면 알려주면 감사하게 배우겠습니다..)

하여 이번 보드는 전부 Signal 로 카파를 깔기로 결정~

'Wiznet > Hardware' 카테고리의 다른 글

| Voltage Level Change of Differential Line According to Termination Resistance Value (0) | 2022.11.28 |

|---|---|

| Ethernet MDI Schematic 설계&실험 (0) | 2022.11.08 |

| Wiznet Ethernet Chip SCH Design Guide - Chip (0) | 2022.11.05 |

| Wiznet W5100S-EVB-TEST 보드 제작기(2) (0) | 2022.11.05 |

| Wiznet Ethernet Chip Design Guide (0) | 2022.11.05 |