Chip 종류별로 다뤄볼 것이지만 먼저 W5500 을 예를 들어 다뤄보도록 하겠다.

모든 자료는 W5500 Datasheet 를 참조하였다.

1. 전원단

먼저 전원단이다. 전원단 VDD, AVDD 는 3.3V 로 설계해야한다.

Supply 전원은 Regulator 를 사용하여 안정적인 전압을 주도록 한다.

Normal Operation Mode일 때 Supply Current 는 132mA 정도 올라가므로 300mA 이상급의 Regulator 사용을 권장한다.

또한, VDD 와 AVDD 는 비드를 통해 연결시켜 구분지어주도록 하는 것을 권장한다.

Bypass Capacitor

표시해 놓은 부분과 같이 Pin 수에 맞게 Bypass Capacitor를 장착해 주는 것을 권장한다.

해당 회로의 메인전원에는 추가로 용량이 큰 전해캡이 설계되어있다.

GND, AGND(=GNDA)

GND와 AGND 를 나눠주면 좋겠지만, AGND 영역을 크게 잡을 수 없다면 차라리 같이 묶는 것을 권장한다.

실제 GND 와 AGND 를 나눠 설계했지만 AGND 영역이 작아 노이즈가 많이 발생해 문제가 생기는 일이 많이 포착됐다고 한다.

XI/CLKIN(=XSCI), XO(=XSCO)

OSC 을 사용한다면 XO 는 NC 처리인 상태로 XI 에만 Clock 을 입력하면 된다.

X-TAL 을 사용한다면 아래 회로대로 설계를 권장한다.

TXN, TXP / RXN, RXP

<Wiznet Ethernet Chip SCH Design Guide> 에서 참고

RSTn

Chip Reset Pin 이다. Active Low 이므로 Pull-up 회로를 구성하여야 안정적으로 동작될 수 있다.

INTn

W5500 Chip에서 인터럽트가 발생하면 알려주는 Pin 이다. Active Low 이므로 Pull-up 회로를 구성하여야 안정적으로 동작될 수 있다.

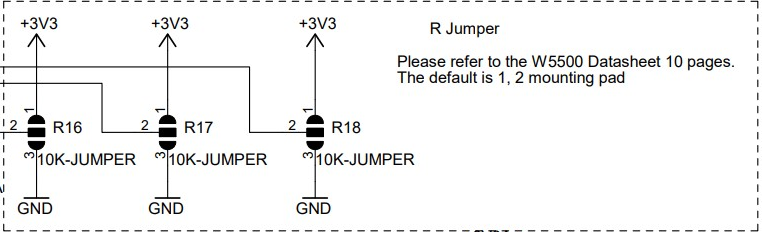

PMODE[2:0] : W5500

<W5500 Datasheet>

W5500 - Network Mode 를 설정하는 Pin 이다.

위 회로와 같이 상황에 따라 변경해서 사용할 수 있도록 구성해도 되고, 값을 고정해서 사용해도 무방하다.

MOD[3:0] : W5100S

<W5100S Datasheet>

Host Interface Mode Select Pin 이다. 이 Chip과 통신할 Host 의 통신방법을 정해준다.

2가지 모드가 있으며, SPI 모드와 Parallel Bus 모드이다.

SPI Mode

Host 와의 통신방법을 SPI 로 정했다면 MOD[3:0] Pin 을 모두 GND 에 연결시켜주고, 위 회로와 같이 연결하여 통신한다.

Parallel Bus Mode

Host 와의 통신방법을 Parallel Bus 로 정했다면 MOD[0,1,3] : GND, MOD[2] : VCC 연결시켜 준 뒤, 위 회로와 같이 연결하여 통신한다.

LED

상태 체크용 LED Pin이다. LED 를 장착하여 상태를 체크할 수 있다. 다른 기능의 Pin으로 호환 불가능

SPI

SPI - SCLK,MOSI,MISO 는 그대로 연결해서 사용. Chip Select Pin 은 Active Low 이기 때문에 Pull-up 저항을 설계해주어야 한다.

ETC Pin

RSVD

RSVD 내부 칩에서 통신을 위해 이미 Fix 되어있는 Pin이다. Open 상태여도 동작하겠지만, Pull-Down 해주는 것을 권장한다.

VBG

반드시 Open 상태로 두어야 한다.

EXRES1

내부 아날로그 회로 바이어싱에 필요한 Pin 이다. AGND 에 Pull-down 으로 12.4k 를 잡아주어야 한다.

TOCAP

내부 신호 안정화용 Pin이다. 반드시 4.7uF 을 장착하여야 한다.

'Wiznet > Hardware' 카테고리의 다른 글

| Voltage Level Change of Differential Line According to Termination Resistance Value (0) | 2022.11.28 |

|---|---|

| Ethernet MDI Schematic 설계&실험 (0) | 2022.11.08 |

| Wiznet W5100S-EVB-TEST 보드 제작기(2) (0) | 2022.11.05 |

| Wiznet W5100S-EVB-TEST 보드 제작기(1) (1) | 2022.11.05 |

| Wiznet Ethernet Chip Design Guide (0) | 2022.11.05 |