제작된 W5100S-EVB-TEST-V1.0 보드의 Compliance Test 를 진행하며 고민하게 된 내용들이다.

Wiznet W5100S-EVB-TEST 보드 제작기(1)

Wiznet Ethernet Chip Design Guide Introduction This document is a Design Guide for WIZnet Chip to be used for PCB. It contains reference for PCB design using W5100, W5300, W5500, W7100A, W7500, and W7500P. Contents of MDI (Medium-de.. alanp.tistory.com 위

uiadu.tistory.com

위 링크는 W5100S-EVB-TEST-V1.0 보드 제작기이다.

[그림1]

회로는 위와 같다. Current Mode PHY 를 사용하기때문에 외부에서 Bias 전압을 잡아주어야 하며, 칩 내부 라인에 터미네이션 저항설계는 되어 있지 않아서 외부에서 설계를 해주어야 한다. 하여, 외부에 터미네이션 저항 100옴을 장착했고, 댐핑저항용으로 3.3옴을 직렬로 장착했다.

[그림2]

조립이 완료되고 기본적으로 Ethernet이 동작되는 것은 확인했다. 그래도 이더넷이 얼마나 안정적으로 동작하는지 확인하기 위해 Compliance Test 를 진행했다.

[그림3]

Compliance Test 를 마쳤다. 100M 대역에서 Test 를 진행했다. 전원소스에 따라 Test 결과가 조금씩 달라지는데, 그 중 가장 괜찮게 됐던 Test 이다. 결과는 Fail , Differential Voltage Level 범위안에 전압레벨이 들어오지 않았다. 약 -115mV 정도 차이가 나는데, 이 정도 수치는 상당히 큰 문제이다.

[그림4]

여기서 한가지 의문이 든다. 혹시 종단 저항인 49.9 옴과 댐핑 저항 3.3옴이 전압분배가 되서 들어가나...?

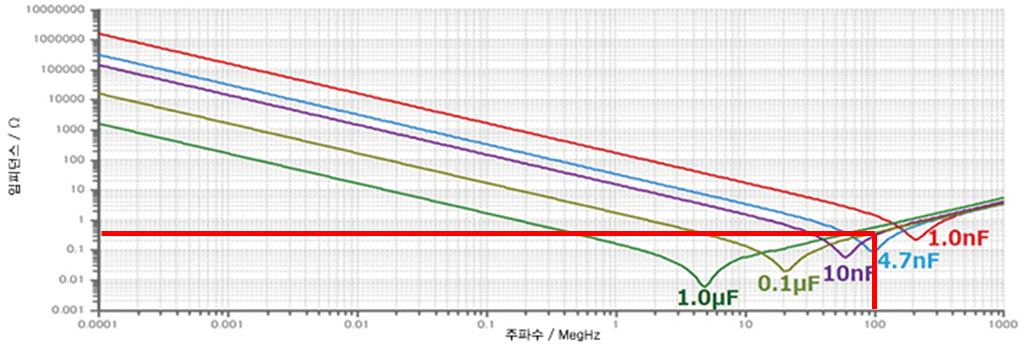

[그림5]

종단저항에 달려있는 Cap은 100M 에선 임피던스가 거의 없는 Short 상태이다.

[그림6]

위의 상황에서 A에선 전압분배가 될테고, B에선 안 될 것이다. 반대인 상황에선 B가 전압분배가 되고, A는 안될 것이다. 항상 Bias 전압기준 + 파형에서는 전압분배가 안 일어나고, - 파형에서만 전압분배가 일어난다.

그렇다면 어쨋든 Differential Voltage Level 은 49.9/53.2 = 0.062 (약 6%) 정도 감소되어 나가게 된다. 라인 하나의 Voltage Peak to Peak 가 1V 라고 봤을때, 약 60mV 감소되는 수치이다.

땡! 다 틀렸다. 그냥 Current Mode 동작이기때문에, 라인 임피던스가 커지면 전압레벨이 작아지는 것이다.

[그림 7]

직렬 댐핑저항을 제거한 후 전압레벨이 올라 거의 통과값 근처까지 온 것을 볼 수 있다.

이 자료를 바탕으로 다시 보드를 제작하기로 했다. 다음 보드의 이름은 W5100S-EVB-TEST-V1.1 이다.

'Wiznet > Hardware' 카테고리의 다른 글

| PoE란 무엇인가? (0) | 2022.12.06 |

|---|---|

| Wiznet W5100S-EVB-TEST 보드 제작기(3) (0) | 2022.11.28 |

| Ethernet MDI Schematic 설계&실험 (0) | 2022.11.08 |

| Wiznet Ethernet Chip SCH Design Guide - Chip (0) | 2022.11.05 |

| Wiznet W5100S-EVB-TEST 보드 제작기(2) (0) | 2022.11.05 |